# Dependable Real-time Infrastructure for Safety-critical Computer

Project number: 869945

Project acronym: De-RISC

http://www.derisc-project.eu/

| D1.1         | Interim platform and domain requirement specification and definition |                            |        |

|--------------|----------------------------------------------------------------------|----------------------------|--------|

| Work Package | WP1                                                                  | Lead Beneficiary           | CG     |

| Туре         | Report                                                               | <b>Dissemination level</b> | Public |

| Due Date     | 31/12/2019                                                           | Version                    | 0.2    |

|              |                                                                      |                            |        |

#### **Brief description**

The purpose of this document is to collect requirements defining technology stack consisting of software architecture, system-on-chip architecture, and PCB board. The document also defines cross-cutting requirements that affect multiple layers in this stack to form a complete requirement set for the Dependable Real-time Infrastructure for Safety-Critical Computer (De-RISC) platform

# **Document control page**

| v                    | Vritten by  |            |

|----------------------|-------------|------------|

| Name                 | Beneficiary | Date       |

| Jan Andersson        | CG          | 18/11/2019 |

| Jimmy Le Rhun        | TRT         | 26/11/2019 |

| Miguel Masmano Tello | FEN         | 03/12/2019 |

| Jaume Aubella        | BSC         | 06/12/2019 |

| David Trilla         | BSC         | 10/12/2019 |

| Nils-Johan Wessman   | CG          | 16/12/2019 |

| Reviewed by   |             |            |

|---------------|-------------|------------|

| Name          | Beneficiary | Date       |

| Jimmy Le Rhun | TRT         | 30/12/2019 |

| Approved by              |             |            |

|--------------------------|-------------|------------|

| Name                     | Beneficiary | Date       |

| Francisco Gómez Molinero | FEN         | 31/12/2019 |

| Change log |            |                      |             |                |

|------------|------------|----------------------|-------------|----------------|

| Version    | Date       | Name                 | Beneficiary | Comments       |

| 0.0        | 18/11/2019 | Jan Andersson        | CG          | Initial draft  |

| 0.1        | 03/12/2019 | Miguel Masmano Tello | FEN         | Internal draft |

| 0.2        | 30/12/2019 | Jimmy Le Rhun        | TRT         | First release  |

Copyright - This document has been produced and funded under the De-RISC H2020 Grant Agreement 869945. Unless officially marked PUBLIC, this document and its contents remain the property of the beneficiaries of the De-RISC Consortium and may not be distributed or reproduced without the express written approval of the project Consortium.

3 / 63

# Disclaimer

This document may contain material that is copyright of certain De-RISC beneficiaries, and may not be reproduced, copied, or modified in whole or in part for any purpose without written permission from the De-RISC Consortium. The commercial use of any information contained in this document may require a license from the proprietor of that information. The information in this document is provided "as is" and no guarantee or warranty is given that the information is fit for any particular purpose. The user thereof uses the information at its sole risk and liability.

The De-RISC Consortium comprises the following partners:

| # | Partner legal name                                                          | Short name        | Acronym | Country |

|---|-----------------------------------------------------------------------------|-------------------|---------|---------|

| 1 | FENT INNOVATIVE SOFTWARE<br>SOLUTIONS SL                                    | fentISS           | FEN     | Spain   |

| 2 | BARCELONA SUPERCOMPUTING<br>CENTER - CENTRO NACIONAL DE<br>SUPERCOMPUTACIÓN | BSC               | BSC     | Spain   |

| 3 | THALES SA                                                                   | THALES            | TRT     | France  |

| 4 | COBHAM GAISLER AB                                                           | COBHAM<br>GAISLER | CB      | Sweden  |

# **Table of contents**

| 1. | Scope of the document                                 | 7  |

|----|-------------------------------------------------------|----|

| 2. | Applicable and reference documents                    | 8  |

|    | Terms, definitions and acronyms                       |    |

|    | 3.1. Terms and definitions                            | 10 |

|    | 3.2. Acronyms                                         | 10 |

| 4. | Introduction                                          | 11 |

|    | 4.1. Requirement format                               | 11 |

| 5. | Global Platform architecture                          | 13 |

|    | 5.1. Hardware platform                                | 13 |

|    | 5.2. Software platform                                | 21 |

|    | 5.3. Preliminary block diagram                        |    |

|    | 5.3.1. Hardware platform                              |    |

|    | 5.3.2. Software platform                              | 23 |

|    | 5.4. Physical and Resource constraints                |    |

|    | 5.5. Environment constraints                          |    |

| 6. | Baseline elements description                         |    |

|    | 6.1. Microprocessor core                              |    |

|    | 6.1.1. Relevant RISC-V standards                      | 28 |

|    | 6.1.2. Processor core overview                        |    |

|    | 6.1.3. NOEL-V subsystem                               | 29 |

|    | 6.1.4. Memory management unit                         |    |

|    | 6.1.5. On-chip debug support                          |    |

|    | 6.2. GRLIB IPs                                        |    |

|    | 6.3. XNG hypervisor overview                          |    |

|    | 6.3.1. XNG configuration                              |    |

|    | 6.3.2. Partitioning                                   |    |

|    | 6.3.3. Partition scheduling                           |    |

|    | 6.3.4. Spatial partitioning                           |    |

|    | 6.3.5. Partition virtual execution environment (PVEE) |    |

|    | 6.3.6. Health monitor                                 |    |

|    | 6.3.7. Inter-partition communication                  |    |

|    | 6.3.8. Delegated I/O devices                          |    |

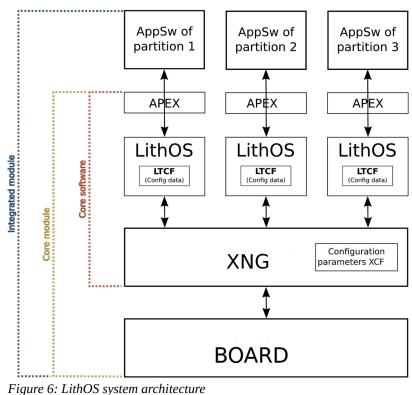

|    | 6.4. LithOS overview                                  | 36 |

|    | 6.4.1. Configuration                                  | 37 |

|    | 6.4.2. Partition management                           |    |

|    | 6.4.3. Process management                             |    |

|    | 6.4.4. Time management                                |    |

|    | 6.4.5. Inter-partition communication                  |    |

|    | 6.4.6. Intra-partition communication                  |    |

|    | 6.4.7. Health Monitor                                 |    |

|    | 6.4.8. Multiple module schedule                       | 40 |

| 6.4.9. Interrupt management                             |    |

|---------------------------------------------------------|----|

| 6.4.10. System management                               |    |

| 6.5. Development tools                                  |    |

| 6.5.1. Gcc + binutils version (CG)                      |    |

| 6.5.2. GRMON debugger                                   |    |

| 6.5.3. xcparser tool                                    |    |

| 7. Detailed sub-systems specification                   |    |

| 7.1. Processor core                                     |    |

| 7.1.1. MMU & privilege levels                           |    |

| 7.1.1.1. Hypervisor support                             |    |

| 7.1.2. Core interface                                   |    |

| 7.1.2.1. Hypervisor and RTOS considerations (FEN)       |    |

| 7.2. Memory subsystem                                   |    |

| 7.2.1. Tightly coupled memory                           |    |

| 7.2.2. L1 cache memory                                  |    |

| 7.2.3. L2 cache memory                                  |    |

| 7.2.4. External memory controller                       |    |

| 7.2.4.1. Fault tolerance properties                     |    |

| 7.2.4.2. Request arbitration                            |    |

| 7.2.5. Global memory mapping                            |    |

| 7.3. Interconnect                                       |    |

| 7.3.1. L1 to L2                                         |    |

| 7.3.2. Main interconnect                                |    |

| 7.3.3. Cache coherency                                  |    |

| 7.3.3.1. Interference channels and isolation properties |    |

| 7.3.3.2. IPC (inter-partition communication) support    |    |

| 7.3.4. IOMMU                                            |    |

| 7.3.4.1. Hypervisor support                             |    |

| 7.4. IO Peripherals                                     |    |

| 7.4.1. UARTs                                            |    |

| 7.4.2. Timers                                           |    |

| 7.4.3. Interrupt controller                             |    |

| 7.4.4. Ethernet                                         |    |

| 7.4.5. DMAs                                             |    |

| 7.4.6. SpaceWire                                        | 60 |

| 7.5. Software architecture                              |    |

| 7.5.1. Time and space partitioning                      |    |

| 7.5.2. Deterministic partition scheduling               |    |

| 7.5.3. Explicit inter-partition communications          |    |

| 7.6. Debug and monitoring                               |    |

| 7.6.1. Debug interface                                  |    |

| 7.6.2. Performance and interference monitoring          |    |

| 7.7. Reset and Boot process                             |    |

| 8. Documentation                                        |    |

|                                                         |    |

# **1. Scope of the document**

The purpose of this document is to collect requirements defining technology stack consisting of software architecture, system-on-chip architecture, and PCB board. The document also defines cross-cutting requirements that affect multiple layers in this stack to form a complete requirement set for the Dependable Real-time Infrastructure for Safety-Critical Computer (De-RISC) platform.

The work has been performed by FentISS (ES), Cobham Gaisler (SE), Barcelona Supercomputing Center (ES), and Thales Research and Technology (TRT).

# 2. Applicable and reference documents

[AD01] ECSS-E-ST-40C, Software general requirements Available at http://www.ecss.nl

[AD02] ECSS-Q-ST-80C, Software product assurance Available at http://www.ecss.nl

[AD03] ECSS-E-ST-20C, Electrical and Electronics Available at http://www.ecss.nl

[AD04] ECSS-E-ST-50-12C , SpaceWire – Links, Nodes Routers and Networks Available at http://www.ecss.nl

[AD05] ECSS-E-ST-50-13C, Interface and communication protocol for MIL-STD-1553B data bus onboard spacecraft, Available at http://www.ecss.nl

[AD06] ECSS-E-ST-50-14C, Spacecraft Discrete interfaces Available at http://www.ecss.nl

[AD07] ECSS-E-ST-50-15C, CANbus extension protocol Available at http://www.ecss.nl

[AD08] ECSS-E-ST-50-51C, SpaceWire – Protocol identification Available at http://www.ecss.nl

[AD09] ECSS-E-ST-50-52C, SpaceWire – Remote Memory Access Protocol Available at http://www.ecss.nl

[AD10] ECSS-E-ST-50-53C, SpaceWire – CCSDS packet transfer protocol Available at http://www.ecss.nl

[AD11] ECSS-E-70-41C, Telemetry and telecommand packet utilization, ECSS-E-70-41c Available at http://www.ecss.nl

[AD12] ECSS-E-ST-10-06, Functional and Technical Specifications Available at http://www.ecss.nl [AD13] ECSS-Q-ST-30-02C, Failure modes, effects and criticality analysis (FMECA) Available at

http://www.ecss.nl

[AD14] ECSS-Q-ST-60-02C, ASIC and FPGA Development Standard Available at http://www.ecss.nl

[AD15] SAVOIR-GS-001 SAVOIR – SAVOIR generic OBC functional spec Available at http://essr.esa.int

[AD16] SAVOIR-GS-002 SAVOIR - Flight Computer Initialisation Sequence Available at http://essr.esa.int

[AD17] ECSS-Q-ST-70C Materials, mechanical parts and processes Available at http://www.ecss.nl [AD18] SAVOIR-TM-002 SAVOIR UART protocol and interface specification Available at http://essr.esa.int

[AD19] ECSS-E-ST-32-10C Structural factors of safety for spaceflight hardware Available at http://www.ecss.nl

[AD20] GRLIB IP Core User's Manual. Available at <u>https://www.gaisler.com/getgrlib</u>

[AD21] Software User Manual – XNG hypervisor. Fent Innovative Software Solutions14-033.009.sum, Issue 7.

[RD01] Avionics Application Software Standard Interface. Part 1 - Required Services. ARINC Specification 653P1-3. Aeronautic Radio, Inc.

[RD02] Avionics Application Software Standard Interface. Part 2 - Extended Services. ARINC Specification 653P2-2. Aeronautic Radio, Inc.

[RD03] Multi-core Processors - Position Paper. Technical Report CAST 32-A, FAA, 2016.

# 3. Terms, definitions and acronyms

# 3.1. Terms and definitions

| Term         | Definition                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Horizon 2020 | It is the biggest EU Research and Innovation programme ever with nearly $\&80$ billion of funding available over 7 years (2014 to 2020) – in addition to the private investment that this money will attract. The purpose of Horizon 2020 is to foster the growth of breakthrough technologies, inventions and advanced developments by the promotion of scientific ideas from the laboratories to the market. |

| RISC-V       | Pronounced "risk-five". It is an open-source hardware instruction set<br>architecture based on established reduced instruction set computer<br>principles.                                                                                                                                                                                                                                                     |

# 3.2. Acronyms

| Acronym | Definition                            |

|---------|---------------------------------------|

| BSC     | Barcelona Supercomputing Center       |

| CG      | Cobham Gaisler                        |

| EC      | European Commission                   |

| EU      | European Union                        |

| ESA     | European Space Agency                 |

| FEN     | fentISS                               |

| H2020   | Horizon 2020                          |

| HW      | Hardware                              |

| ISA     | Instruction Set Architecture          |

| NoC     | Network-on-Chip                       |

| RISC    | Reduced Instruction Set Computer      |

| RISC-V  | Reduced Instruction Set Computer Five |

| SoC     | System-on-Chip                        |

| SW      | Software                              |

| TC      | Telecommand                           |

| TM      | Telemetry                             |

| TRL     | Technology Readiness Levels           |

| TRT     | Thales Research & Technology          |

| WP      | Work Package                          |

# 4. Introduction

The De-RISC platform to be developed within this project consists of three levels:

- Software architecture: Software environment consisting of the XtratuM Hypervisor and the LithOS Operating System.

- System-on-Chip (SoC) architecture: Digital hardware design consisting of general-purpose microprocessors, peripherals, communication controllers and interconnect

- De-RISC FPGA board: Implementation of SoC architecture in programmable logic on a custom PCB board.

This requirement specification has the following structure:

- Section 5 is the coarse-grain view of the platform

- Section 6 describes the existing building blocks used for the platform

- Section 7 details specific functional units to be developed/adapted, consolidating requirements for both hardware, software and (non)functional properties in the same place to ensure consistency.

# 4.1. Requirement format

The following table describes the wording used for the requirements specification:

| Shall  | The word "Shall" in the text expresses a mandatory requirement of the specification.                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Should | The word "Should" in the text expresses a recommendation or advice on implementing such a requirement of the specification.                                            |

| Must   | The word "Must" in the text is used for legislative or regulatory requirements (e.g. health and safety). It is not used to express a requirement of the specification. |

| Will   | The word "Will" in the text denotes a provision or service or an intention in connection with a requirement of the specification.                                      |

| May    | The word "May" in the text expresses a permissible practice or action. It does not express a requirement of the specification.                                         |

| N/A | Not applicable. |

|-----|-----------------|

|-----|-----------------|

The following template shall be used for the formulation of requirements:

| <identifier></identifier>                                                                       | <requirement according="" description="" smart<="" th="" the="" to=""></requirement> |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| DeRISC-T1.x-AA-ID000                                                                            | criteria "Specific Measurable Acceptable Realistic and<br>Time-bound">               |

| <status></status>                                                                               | e.g.                                                                                 |

| {proposed, accepted, rejected}                                                                  | The demonstrator shall                                                               |

| <qualification method=""> e.g. black box test, (code) inspection, demonstration</qualification> |                                                                                      |

| <rationale></rationale>                                                                         |                                                                                      |

| <comment></comment>                                                                             |                                                                                      |

#### T1.X = task number

#### ID000 = requirement ID number

| ID0xx | Fentiss        |

|-------|----------------|

| ID1xx | Cobham Gaisler |

| ID2xx | BSC            |

| ID3xx | Thales         |

#### AA = Requirement type

| Functional Requirements          | FU |

|----------------------------------|----|

| Input/Output Requirements        | IO |

| Hardware Requirements            | HW |

| Software Requirements            | SW |

| Mechanical/Physical Requirements | ME |

| Performance Requirements         | PR |

| Safety Requirements              | SA |

| Security Requirements            | SE |

|                                  |    |

|                                  |    |

# 5. Global Platform architecture

# 5.1. Hardware platform

| DeRISC-T1.1/T1.2-FU-ID100           | The De-RISC FPGA platform shall be available as a                    |  |

|-------------------------------------|----------------------------------------------------------------------|--|

| proposed                            | package of software that can be used together with the De-RISC board |  |

| Qualification method: Demonstration |                                                                      |  |

| Rationale:                          |                                                                      |  |

| Comment:                            |                                                                      |  |

| DeRISC-T1.1/T1.4-HW-ID100<br>proposed                                                                                                                                   | The De-RISC SoC shall be implemented in programmable logic (FPGA) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Qualification method: Inspection                                                                                                                                        |                                                                   |

| Rationale: FPGA technology is the only feasible target technology within the project timeline.<br>FPGAs also allows application specific adaptations of the SoC system. |                                                                   |

| Comment: The choice of target FPGA will be settled for the final issue of this document.                                                                                |                                                                   |

| DeRISC-T1.1-HW-ID101                                                                                                                                                                                                                                                                                                                                 | The SoC design shall implement at least four                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| proposed                                                                                                                                                                                                                                                                                                                                             | microprocessor cores                                                                                                   |

| Qualification method: Inspection                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |

| Rationale: Addition of additional four cores provides additional computational performance<br>where target technologies are often limited in maximum frequency. Current applications within<br>space use multi-core systems to achieve higher integration where independent software<br>functions run on separate cores within one processor device. |                                                                                                                        |

| -                                                                                                                                                                                                                                                                                                                                                    | r cores affect how much logic that is required on the target<br>FPGA selection and FPGA selection may limit the number |

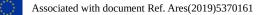

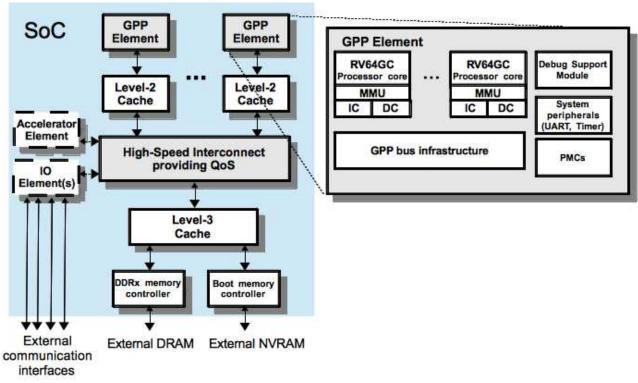

| DeRISC-T1.1-HW-ID102                | The SoC topology should match the topology put forth in the De-RISC proposal:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| proposed                            | SoC GPP Level-2<br>Level-2<br>Cache<br>High-Speed Interconnect<br>providing QoS<br>Level-3<br>Cache<br>DDRx memory<br>bot memory<br>bot memory<br>sternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>controller<br>ternal<br>controller<br>ternal<br>cache<br>ternal<br>controller<br>ternal<br>cache<br>ternal<br>controller<br>ternal<br>cache<br>ternal<br>controller<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>ternal<br>cache<br>terna |

| Qualification method: Inspection    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rationale: Re-use of building block | s places requirements on topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Comment:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DeRISC-T1.1-HW-ID103                                                                    | The general purpose microprocessor core shall                   |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| proposed                                                                                | implement the RISC-V 64-bit ISA with the GC (IMAFDC) extensions |

|                                                                                         |                                                                 |

| Qualification method: Demonstratic                                                      | on                                                              |

| Rationale: G has been identified in                                                     | ESA studies as the required feature set to match existing       |

| space-grade processors. C improves memory utilization and possibly performance for some |                                                                 |

| applications. A is required for multi-                                                  | -core applications.                                             |

| Comment:                                                                                |                                                                 |

| Comment.                                                                                |                                                                 |

| DeRISC-T1.1-HW-ID104                                                                       | The general purpose microprocessor should implement |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------|

| proposed                                                                                   | the RISC-V N extension                              |

| Qualification method: Demonstrati                                                          | on                                                  |

| Rationale: N is likely to be found to be required however few other implementations exist. |                                                     |

| Comment:                                                                                   |                                                     |

|                                                                                            |                                                     |

| DeDISC T1 1 HW ID105                                                                       |                                                     |

| DeRISC-11.1-HW-ID105                                           | The general purpose microprocessors shall implement a |  |

|----------------------------------------------------------------|-------------------------------------------------------|--|

| proposed                                                       | Memory Management Unit                                |  |

| Qualification method: Demonstration                            |                                                       |  |

| Rationale: MMU is required to run target software environments |                                                       |  |

| Comment:                                                       |                                                       |  |

| DeRISC-T1.1-HW-ID106                                                                                                                        | The hardware platform shall maintain cache coherency |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| proposed                                                                                                                                    | between L1 caches within a GPP element.              |

| Qualification method: Demonstration                                                                                                         |                                                      |

| Rationale: Hardware assisted cache coherency reduces effort for SW. Legacy software from the space domain may depend on this functionality. |                                                      |

| Comment: Current building blocks make use of bus snooping. Driving the selection of interconnect.                                           |                                                      |

| DeRISC-T1.1-HW-ID107                             | The interconnect between the GPP elements and Level-2 |

|--------------------------------------------------|-------------------------------------------------------|

| proposed                                         | cache shall be based on AMBA2 AHB.                    |

| Qualification method: Inspection                 |                                                       |

| Rationale: Required for hardware cache coherency |                                                       |

| Comment:                                         |                                                       |

| DeRISC-T1.1-HW-ID104                                                                                            | The interconnect between the GPP elements and Level-2                                  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| proposed                                                                                                        | cache should make use of multi-level buses to reduce interference in the general case. |

| Qualification method: Inspection                                                                                |                                                                                        |

| Rationale: Multi-layer address-striped interconnect has been measured to improve average processing performance |                                                                                        |

| Comment:                                                                                                        |                                                                                        |

| DeRISC-T1.1/T1.4-HW-ID108                                                                                                                                                                                                                           | The De-RISC platform shall support use of external  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| proposed                                                                                                                                                                                                                                            | DDR2, DDR3, or DDR4 SDRAM as primary/working memory |

| Qualification method: inspection                                                                                                                                                                                                                    |                                                     |

| Rationale: DDR2/3/4 SDRAM is required for bandwidth and required memory density (size) for space applications.                                                                                                                                      |                                                     |

| Comment: Considering that the FPGA implementation will be limited in maximum operating frequency there could be a case for use of SSRAM running synchronously with the system clock. However SSRAM has lower memory density compared to DDRx SDRAM. |                                                     |

| DeRISC-T1.1/T1.4-HW-ID109                                                                                    | The platform shall support use of external parallel non- |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| proposed                                                                                                     | volatile memory (NOR Flash, MRAM)                        |

| Qualification method: Inspection                                                                             |                                                          |

| Rationale: Parallel NOR Flash and parallel MRAM are traditionally used for boot memory in space applications |                                                          |

Comment: While the platform shall support use of parallel memory it is not required that this type of memory components are mounted on the De-RISC board.

| DeRISC-T1.1/T1.4-HW-ID110                                                                                                                                                                                                                                                                                                                                                        | The platform shall support use of external SPI non- |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| proposed                                                                                                                                                                                                                                                                                                                                                                         | volatile memory as boot memory.                     |

| Qualification method: Inspection                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| Rationale: High-reliability SPI memory devices exist and can provide smaller form factor compared to parallel versions.                                                                                                                                                                                                                                                          |                                                     |

| Comment: Boot from SPI can be implemented either through a SPI memory controller that provides a memory-mapped view of the external device or through use of a boot ROM that makes use of software and a traditional SPI controller. While the platform shall support use of SPI memory it is not required that this type of memory components are mounted on the De-RISC board. |                                                     |

| DeRISC-T1.1/T1.4-HW-ID111                                                                                                      | The platform shall support high-capacity non-volatile |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| proposed                                                                                                                       | storage in NAND Flash                                 |

| Qualification method: Inspection                                                                                               |                                                       |

| Rationale: NAND Flash is the only currently used non-vol technology that can offer gigabyte of storage for space applications. |                                                       |

Comment: While the platform shall support use of NAND Flash memory it is not required that this type of memory components are mounted on the De-RISC board.

| DeRISC-T1.1/T1.4-HW-ID112<br>proposed                                                                                                                                                                                                 | The platform shall provide at least two Gigabit Ethernet interfaces |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Qualification method: Inspection                                                                                                                                                                                                      |                                                                     |

| Rationale: Ethernet is a convenient debug link and is widely used in automotive and aerospace applications. NASA has through the Lunar missions used Ethernet for new platforms. The European Ariane6 computer makes use of Ethernet. |                                                                     |

| Comment: Number of Ethernet interface supported by the FPGA board will be limited by                                                                                                                                                  |                                                                     |

#### FPGA and board space.

| DeRISC-T1.1/T1.4-HW-ID113                                                                          | The platform shall provide at least two SpaceWire |  |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| proposed                                                                                           | interfaces each with a like rate of 200 Mbit/s    |  |

| Qualification method: Demonstratio                                                                 | n                                                 |  |

| Rationale: SpaceWire is widely used in space applications                                          |                                                   |  |

| Comment: Number of interfaces supported by the FPGA board will be limited by FPGA and board space. |                                                   |  |

| DeRISC-T1.1/T1.4-HW-ID114                                                                      | Hardware shall provide routing between the SpaceWire |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|

| proposed                                                                                       | interfaces                                           |

| Qualification method: Demonstratio                                                             | n                                                    |

| Rationale: Routing functionality is provided by existing space-grade devices (GR740)           |                                                      |

| Comment: SpW router/switch functionality is intended, as opposed to routing implemented by SW. |                                                      |

| DeRISC-T1.1/T1.4-HW-ID115                                                  | The platform shall provide at least two SpaceFibre |

|----------------------------------------------------------------------------|----------------------------------------------------|

| proposed                                                                   | interfaces with a rate of 2Gbit/s                  |

| Qualification method: Inspection                                           |                                                    |

| Rationale: High-Speed serial links are being adopted in space applications |                                                    |

| Comment:                                                                   |                                                    |

| DeRISC-T1.1/T1.4-HW-ID116 | The platform shall provide at least two CAN-FD |

|---------------------------|------------------------------------------------|

| proposed                  | interfaces                                     |

#### Qualification method: Inspection

#### Rationale: CAN is seeing adoption in space and aerospace

Comment:

| DeRISC-T1.1/T1.4-HW-ID117                                               | The platform's CAN interfaces need to be connected to |

|-------------------------------------------------------------------------|-------------------------------------------------------|

| proposed                                                                | at least two separate CAN controllers                 |

| Qualification method: Inspection                                        |                                                       |

| Rationale: ESA CAN redundancy requirements require separate controllers |                                                       |

| Comment:                                                                |                                                       |

| DeRISC-T1.1/T1.4-HW-ID118                                             | The platform shall provide at least two UART interfaces |

|-----------------------------------------------------------------------|---------------------------------------------------------|

| proposed                                                              |                                                         |

| Qualification method: Inspection                                      |                                                         |

| Rationale: UART remains a common interface to avioincs subsystems     |                                                         |

| Comment: RS422 or RS485 needs to be selected for board implementation |                                                         |

| DeRISC-T1.1/T1.4-HW-ID119                                                             | The platform shall allow extensions to support MIL- |

|---------------------------------------------------------------------------------------|-----------------------------------------------------|

| proposed                                                                              | STD-1553B                                           |

| Qualification method: Inspection                                                      |                                                     |

| Rationale: MIL-STD-1553B is widely used in aerospace and space applications           |                                                     |

| Comment: It shall be demonstrated that the system can be extended with MIL-STD-1553B  |                                                     |

| controllers. MIL-STD-1553 transceivers occupy a large amount of board space and it is |                                                     |

considered infeasible to support the bus on the current iteration of the De-RISC board.

| DeRISC-T1.1/T1.4-HW-ID120        | The platform shall provide at least one general-purpose |

|----------------------------------|---------------------------------------------------------|

| proposed                         | SPI interface capable of master and slave mode          |

| Qualification method: Inspection |                                                         |

| Rationale:                       |                                                         |

| Comment:                         |                                                         |

| DeRISC-T1.1/T1.4-HW-ID121        | The platform shall growide at least one I2C has interface |

|----------------------------------|-----------------------------------------------------------|

| proposed                         | The platform shall provide at least one I2C bus interface |

| Qualification method: Inspection |                                                           |

| Rationale:                       |                                                           |

| Comment:                         |                                                           |

| DeRISC-T1.1-HW-ID122             | The platform shall include an I/O memory management |

|----------------------------------|-----------------------------------------------------|

| proposed                         | unit (IOMMU)                                        |

| Qualification method: Inspection |                                                     |

| Rationale:                       |                                                     |

| Comment:                         |                                                     |

# 5.2. Software platform

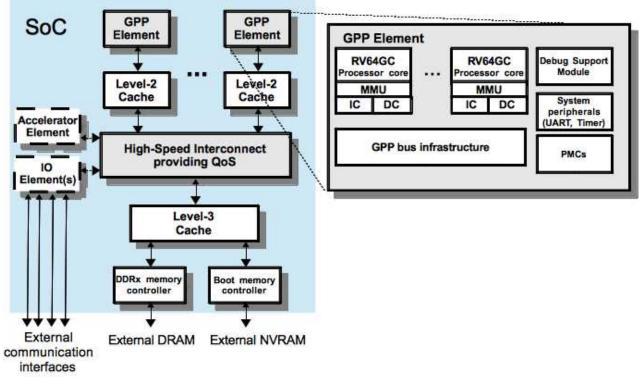

| DeRISC-T1.1-SW-ID000                                      | The De-RISC platform shall include a partitioning kernel                     |

|-----------------------------------------------------------|------------------------------------------------------------------------------|

| proposed                                                  | based on a hypervisor and, at partition level a runtime or operating system. |

| Qualification method: Pavian of the Do PISC documentation |                                                                              |

Qualification method: Review of the De-RISC documentation.

Rationale: A partition kernel allows to run multiple software systems in single platform. Currently, it is the approach being used for implementing IMA-based systems in the aerospace sector.

Comment:

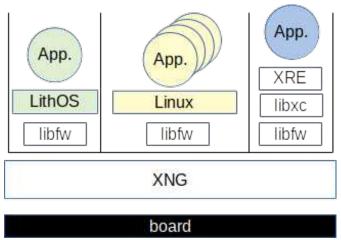

| DeRISC-T1.1-SW-ID001                                                                       | The De RISC plotform's hypervisor shall be VNG  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------|

| proposed                                                                                   | The De-RISC platform's hypervisor shall be XNG. |

| Qualification method: Review of the De-RISC documentation.                                 |                                                 |

| Rationale: XNG was the selected hypervisor for building the proposed De-RISC architecture. |                                                 |

| Comment: XNG is qualified as ECSS software criticality class B.                            |                                                 |

| DeRISC-T1.1-SW-ID002                                                                                                                                          | The De-RISC platform's runtimes and operating system, |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| proposed                                                                                                                                                      | at partition level, shall be LithOS and XRE.          |

| Qualification method: Inspection                                                                                                                              |                                                       |

| Rationale: LithOS and XRE were the selected operating system and runtime for being used at partition level as component of the proposed De-RISC architecture. |                                                       |

Comment: Both, LithOS and XRE, are qualified as ECSS software criticality class B.

| DeRISC-T1.1-SW-ID003             | The De-RISC platform shall allow mixing applications |

|----------------------------------|------------------------------------------------------|

| proposed                         | with different criticallity level.                   |

| Qualification method: Inspection |                                                      |

| Rationale:                       |                                                      |

| Comment:                         |                                                      |

| DeRISC-T1.1-SW-ID004                                                                                                                         | The De-RISC platform shall be qualified according to                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| proposed                                                                                                                                     | the ECSS E40 [AD01] and Q80 [AD02] standard for the software criticality class B. |  |

| Qualification method: Verification of the resulting ECSS qualification package.                                                              |                                                                                   |  |

| Rationale: The DeRISC software platform requires to reach a high software criticality class for being eligible candidate for space missions. |                                                                                   |  |

| Comment:                                                                                                                                     |                                                                                   |  |

5.3. Preliminary block diagram

# 5.3. Preliminary block diagram

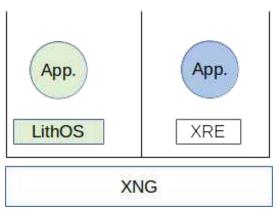

### 5.3.1. Hardware platform

Figure 1: De-RISC hardware platform

#### 5.3.2. Software platform

Figure 2: De-RISC software platform

Copyright - This document has been produced and funded under the De-RISC H2020 Grant Agreement 869945. Unless officially marked PUBLIC, this document and its contents remain the property of the beneficiaries of the De-RISC Consortium and may not be distributed or reproduced without the express written approval of the project Consortium.

23 / 63

# 5.4. Physical and Resource constraints

| DeRISC-T1.1/T1.4-ME-ID102                                                                                                                                                                      | The De DISC EDGA beard should have a 211 form faster  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| proposed                                                                                                                                                                                       | The De-RISC FPGA board should have a 3U form factor   |  |

| Qualification method: Inspection                                                                                                                                                               |                                                       |  |

| Rationale: 3U is considered a preferred form factor according to space industry surveys performed by Cobham Gaisler.                                                                           |                                                       |  |

| Comment: FPGA power circuitry and transceivers could drive the design to a 6U form factor.<br>PC104 would be relevant for cubesats but is considered unfeasible for the proposed architecture. |                                                       |  |

|                                                                                                                                                                                                |                                                       |  |

| DeRISC-T1.1/T1.4-ME-ID102                                                                                                                                                                      | The De-RISC FPGA board should a mass of less than 1.2 |  |

| proposed                                                                                                                                                                                       | kg                                                    |  |

| Qualification method: Measurement                                                                                                                                                              |                                                       |  |

| Rationale:                                                                                                                                                                                     |                                                       |  |

Comment:

| DeRISC-T1.1/T1.4-ME-ID102      | The De-RISC FPGA board should dissipate less than 10                     |

|--------------------------------|--------------------------------------------------------------------------|

| proposed                       | W when operating in worst case configuration and at maximum performance. |

| Qualification method: Analysis |                                                                          |

| Rationale:                     |                                                                          |

| Comment:                       |                                                                          |

# 5.5. Environment constraints

| DeRISC-T1.1/T1.4-ME-ID103                                | The De-RISC FPGA platform shall be designed in order<br>to ensure that nominal performances are maintained w/o<br>degradation in presence of (limited) radiation effects as: |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | Total Ionizing radiation dose (TID), including NIEL damage,                                                                                                                  |

|                                                          | Single Event Latch-up (SEL),                                                                                                                                                 |

| proposed                                                 | Single Event Upset (SEU),                                                                                                                                                    |

|                                                          | Burn-Out,                                                                                                                                                                    |

|                                                          | Single Event Gate Rupture (SEGR),                                                                                                                                            |

|                                                          | Single Event Transient (SET),                                                                                                                                                |

|                                                          | Single Event Functional Interrupt (SEFI)                                                                                                                                     |

|                                                          |                                                                                                                                                                              |

| Qualification method: Analysis                           |                                                                                                                                                                              |

| Rationale: Board shall be usable for flight applications |                                                                                                                                                                              |

| Comment:                                                 |                                                                                                                                                                              |