The first RISC-V, fully European platform for space

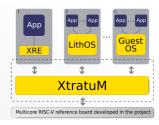

RISC-V multi-core platform and hypervisor for time and space isolation for applications within space and aeronautical domains.

www.derisc-project.eu

## **GOALS**

- No US export restriction

- Multi-core interference mitigation

- Portability

- Fault-tolerance

- Open standards

- H2020 De-RISC

Dependable Real-time Infrastructure

for Safety-critical Computer

De-RISC will deliver a complete stack with a fault-tolerant RISC-V multi-processor system-on-chip (MPSoC) design together with qualified hypervisor software, available for use on a CPCI Serial Space development board.

- Strengthen European leadership in the supply of Integrated Modular Avionics HW/SW.

- 2 Consolidate the European position in real-time embedded processors technology.

- 3 Capitalize on the economy of scale by reinforcing an open standard Instruction Set Architecture (ISA) for the embedded market.

## Hardware development

On the hardware side, De-RISC will integrate an MPSoC composed of NOEL-V cores from Cobham Gaisler including safety-critical hardware support (monitoring units and contention control) by Barcelona Supercomputing Center, ready for space applications providing them with the required level of performance.

## Software development

On the software side, De-RISC will provide the XtratuM hypervisor from Fent Innovative Software Solutions (fentISS) and a representative modular application from Thales Research & Technology.

THALES

This project has received funding from the European Union's Horizon 2020 Research and Innovation Programme under Grant Agreement EIC-FTI 869945