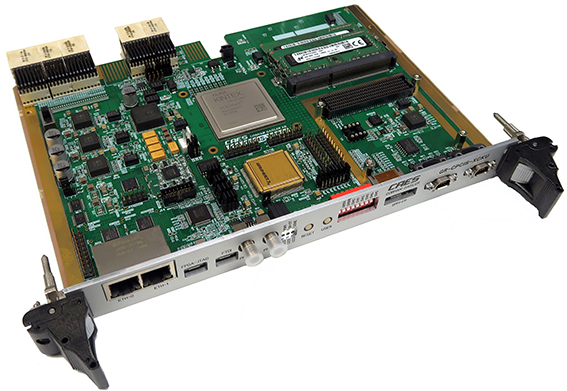

The De-RISC project develops a platform consisting of the fentISS XNG hypervisor running on a multi-processor system-on-chip design with the NOEL-V RISC-V processor. The project has developed the hardware/software stack using FPGA implementations of the system-on-chip design and the project has developed a custom FPGA board to be able to demonstrate the use of strong error-detection and correction on the external DDR3 SDRAM interface and to have a development platform with a larger amount of communication interfaces available.

The FPGA board developed in the project is now being commercialized by under the product name GR-CPCIS-XCKU. A product web page is available at the Cobham Gaisler site.

Work within the De-RISC project continues using the development board where radiation tests are scheduled to take place within the coming two months.