The De-RISC project develops a platform consisting of several elements:

- The fentISS XtratuM hypervisor

- The De-RISC SoC design, which is a multi-processor system featuring the NOEL-V RISC-V RV64GCH processor core and several communication interfaces

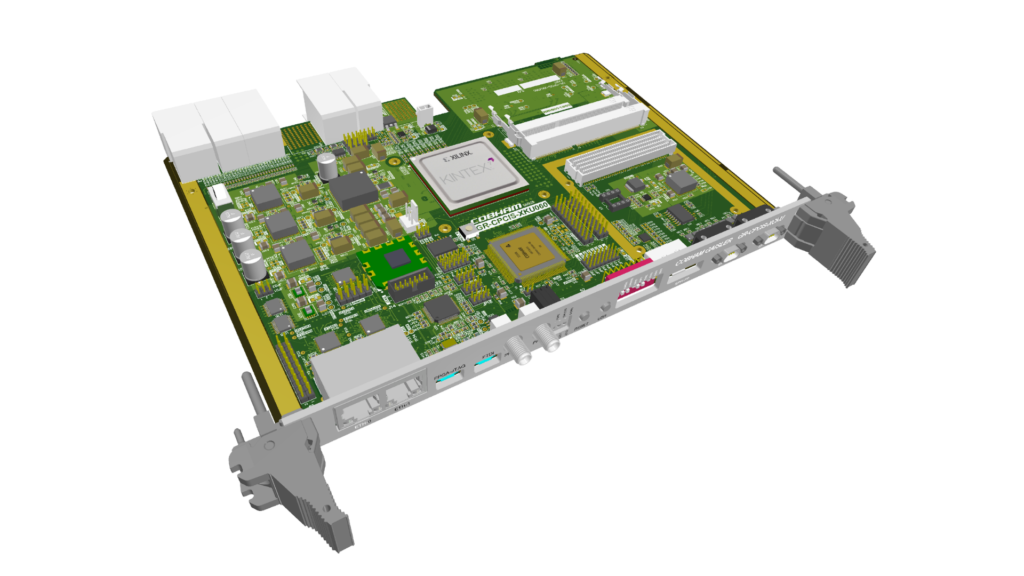

- The De-RISC FPGA board

The De-RISC FPGA board is developed within the project to provide a hardware platform to demonstrate the capabilities of the SoC design and software developed within the project. Existing FPGA prototype boards were deemed to have a to large delta compared to a design that would be applied in space applications, lacked support for the platform’s communication interfaces, or specific FPGA.

The first De-RISC board is currently in assembly and commercial availability is expected in Q4 2021.

The De-RISC FPGA board is intended to be used in a system with a cPCI Serial Space backplane. The board can also be used standalone for bench top development. The board has a Xilinx Kintex UltraScale XCKU060 FPGA together with a GR716 microcontroller.

The FPGA on the board is susceptible to single event upsets (bit flips) in its configuration memory and protecting the design implemented in the FPGA fabric against these radiation effects requires scrubbing the FPGA configuration memory to prevent accumulation of errors. This is done through the inclusion of the radiation hardened GR716 microcontroller on the FPGA board. The microcontroller acts as a supervisor to the FPGA and can prevent accumulation of errors.

Due to the use of commercial and prototype grade components on the board, the De-RISC FPGA board is not suitable for operation in a space environment. Instead, the focus has been to develop a prototype board and to identify components required to make a flight version of the board, which is likely to require a redesign of the PCB to meet mission requirements.

The backplane interfaces of the board are:

- Two-lane SpaceFibre for full-mesh interconnect using FPGA GTH banks

- SpaceWire for dual-star interconnect

- Dual-redundant CAN-bus to FPGA and/or GR716 via two or four transceivers

- SGPIO and I2C connected to FPGA with jumper-configurable pull-ups

- 12V supply from backplane that can be turned off by the external input PS_ON#

- Other utility signals connected to the FPGA

The front-panel interfaces are:

- 2x RJ45 to FPGA via magnetics and Gbit Ethernet transceivers. RGMII interface to FPGA.

- 1x eSATA for SpaceFibre to FPGA via CML redriver.

- 2x MDM9 for SpaceWire via LVDS transceivers/repeaters to FPGA.

- Status LEDs, push-buttons and switches (not included in Figure 1).

- A 2×10 connector to interface with a GR-ACC-6U_6UART breakout board providing access to 6 UARTS (or 16 GPIOs).

- 2xSMA or 2xSMB for PPS time distribution to FPGA.

- 2xUSB ports for

- JTAG access to FPGA and FMC (separate chains)

- GR716 debug UART and two FPGA UARTs

The De-RISC board will be available from Gaisler, both as a generic FPGA development board and pre-programmed with the De-RISC SoC design.