ABOUT US

The De-RISC (Dependable Real-time Infrastructure for Safety-critical Computer) project addresses computer systems within the space and aviation domains. De-RISC – Dependable Real-time Infrastructure for Safety-critical Computer – is a proposed project where an international consortium will introduce a hardware and software platform based around the RISC-V ISA. The work proposed in this project is to productize a multi-core RISC-V system-on-chip design already owned by Cobham Gaisler and to port the XtratuM hypervisor owned by fentISS to that design to create a full platform consisting of hardware and software for future European developments within space and aeronautical applications.

THE NEED

The space market is growing rapidly with a wide range of new technology and computer-based services becoming available to society. Just as in other domains, there are requirements on more functionality and higher integration and this in turn requires improved computing performance, and methods to ensure safe and reliable software (SW) execution, by using virtualization techniques such as hypervisors. Computer cores implement an Instruction Set Architecture (ISA) as a specification of their functionality, their “machine language”. By following the ISA it is possible to write a software application for a processor. There are several processor vendors in the

market offering non-compatible products, and some are subject to US export regulations. Examples of processor implementations with different ISAs are the x86, MIPS and ARM architectures (consumer electronics), PowerPC (military, space and aerospace) and SPARC (space). The world market for aviation and space systems faces a significant shift caused by the loss of momentum of the traditionally used PowerPC and SPARC systems in the commercial domain. This means that the space industry is not able to leverage software from the commercial domain and this fuels a need to shift to architectures present in the, larger, commercial markets.

TECHNOLOGY OPPORTUNITY

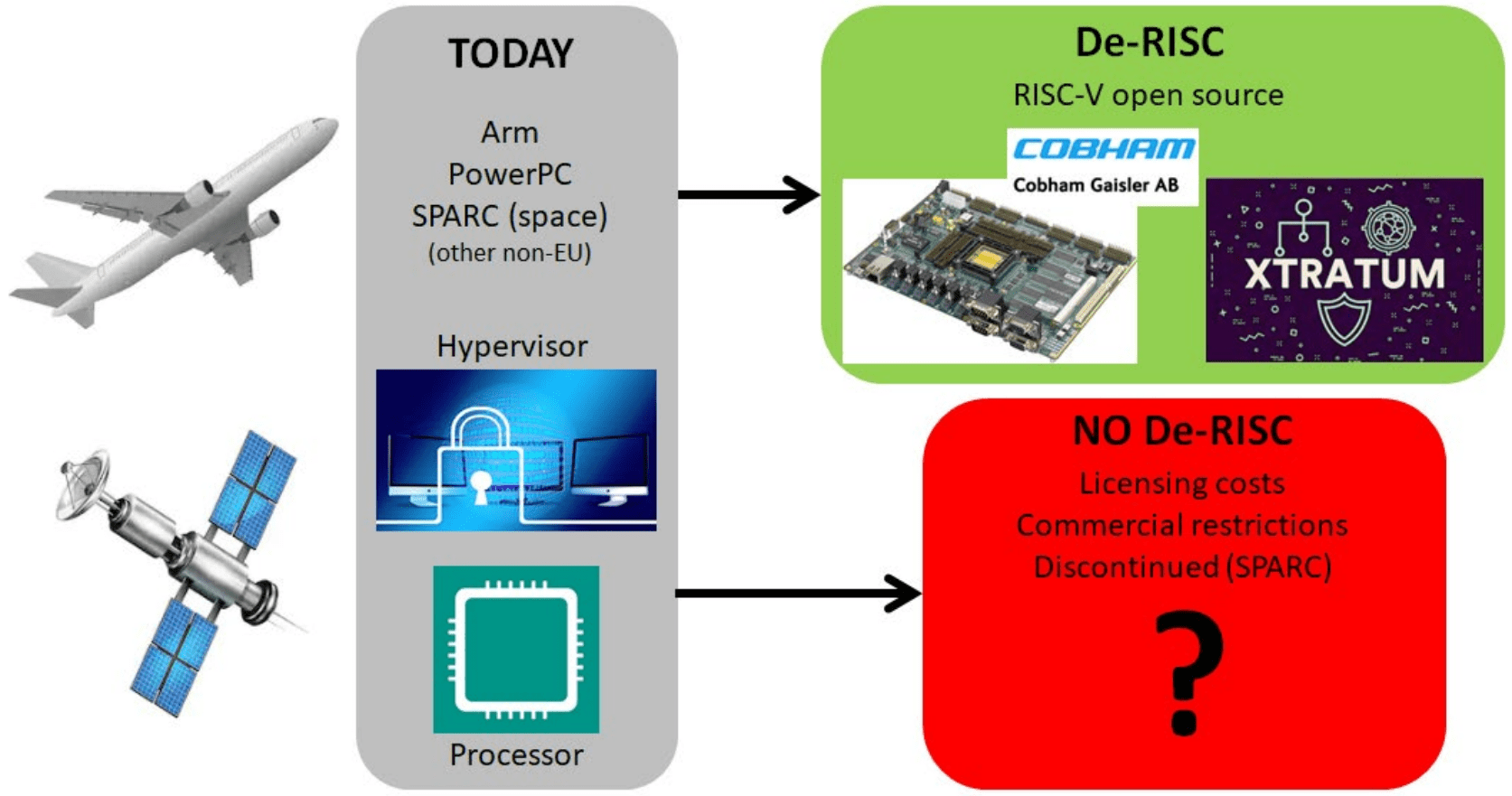

Recently, an open-source Instruction Set Architecture (ISA) called RISC-V has become extremely popular and it is supported by a plethora of companies and research institutions. To some extent, RISC-V is at hardware (HW) level what Linux was in its origins at Operating System level, offering a competitive open source platform able to compete with Windows-based products. Thus, RISC-V offers a unique opportunity to develop EU-based products for the aviation and space domains with no dependence on external technology or licenses, and tailored to fulfill the requirements of critical embedded systems by means of a hypervisor fully developed in Europe as is the case of XtratuM. And it is now, when those RISC-V products do not exist yet anywhere, when the opportunity to develop them and gain a strategic commercial position arises. In particular, this technology will be increasingly adopted in aircraft and space systems starting their design process in the following 2 years, thus replacing a significant fraction of non-EU technology in the short term, and the vast majority of those processors and hypervisors in the mid-term for the most critical systems and for the mixed-critical systems (figure).

Figure: Scenario today and future perspectives

The outcome of De-RISC is both a flight computer prototype board supported by the XtratuM software package and building blocks to be used in further exploitation of the project results. Customers will thus have access to a higher-performance, flexible, extensible, non-export restricted, avionics and space compliant platform.

De-RISC brings critical features to the market that make it unique in front of the competition:

1. No US export restrictions: most existing products use US technology, thus subject to US export control. De-RISC’s IP core platform and software will not be subject to any US regulatory influence by building on RISC-V.

2. Multi-core interference mitigation concepts by Barcelona Supercomputing Center – Centro Nacional de Supercomputación integrated in the RISC-V SoC and validated by Thales Research & Technology become a unique feature, and will provide a key advantage w.r.t. competitors by limiting drastically interference while preserving high-performance operation.

3. Portability: The proposed development will create a RISC-V HW/SW platform that can be implemented in FPGAs and application specific standard products. This provides an edge for integrators that can adapt their choice of implementation technology based on mission requirements.

4. Fault-tolerance concepts: The platform will be provided by companies with experience in the space domain and with heritage in design of fault-tolerant systems.

5. Future-proof selection for new platforms: New software products are not being ported to SPARC and PowerPC architectures. With an established vendor providing a RISC-V platform there are guarantees of continued support for the hardware platform while developments from the commercial domain for the RISC-V architecture can be leveraged over time.

HARDWARE DEVELOPMENT

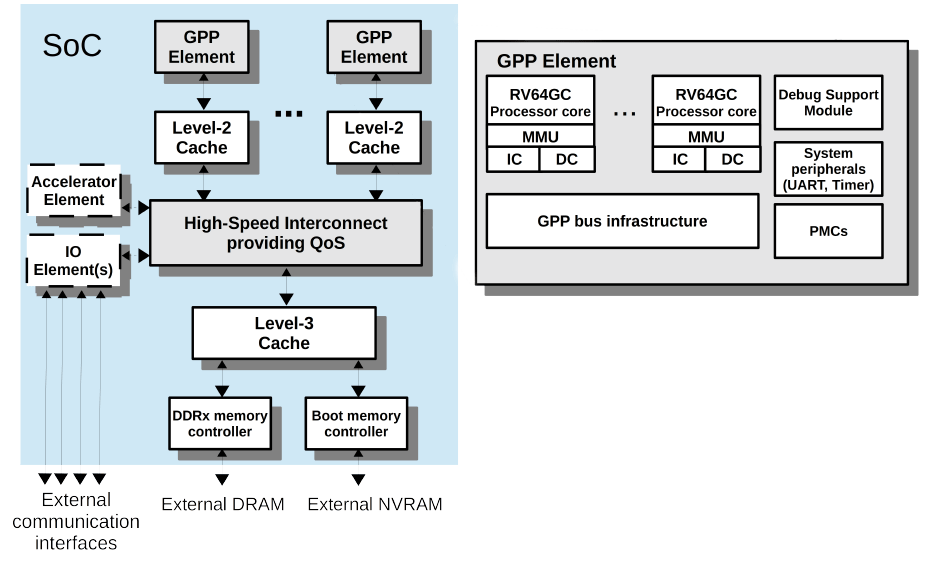

On the hardware side, De-RISC will integrate an MPSoC composed of NOEL-V cores from Cobham Gaisler including safety-critical hardware support (monitoring units and contention control) by Barcelona Supercomputing Center, ready for space applications providing them with the required level of performance.

SOFTWARE DEVELOPMENT

On the software side, De-RISC will provide the XtratuM hypervisor from Fent Innovative Software Solutions (fentISS) and a representative modular application from Thales Research & Technology.